コンピュータ・アーキテクチャ屋からみた 量子コンピュータ・システム

九州大学 システム情報科学研究院 谷本輝夫

# 自己紹介

私の研究アプローチ(コンピュータ・アーキテクチャ)

## ハードウェア・ソフトウェア協調設計による 計算機システムの全体最適化

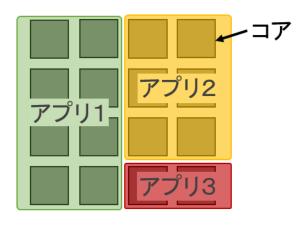

マルチコアプロセッサ活用

[IEEE PACT '14]

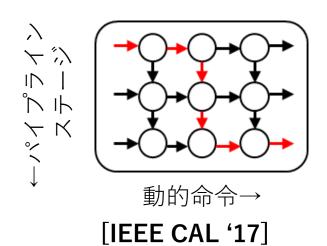

プロセッサ性能モデル解析

新デバイス(SFQ)活用 コンピューティング

[IEEE VLSI '20] [IEEE MICRO '20]

## アーキテクチャ屋の役割とは?

### 次世代計算機システム(応用+SW+HW)を探求!

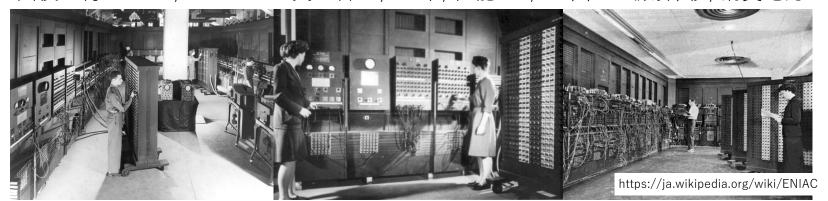

#### 1946年 世界最初の電子計算機ENIAC

設置面積:約167 m2, デバイス:真空管17,468本, 性能:5,000回の加減算/秒, 消費電力150KW

面積 1/20万、デバイス数100万倍、性能25×106倍、消費電力1/500 劇的な境界条件の変化が計算機の姿と応用(そして社会までも)を変える!

#### 2017年 Tesla V100 GPU (Voltaマイクロアーキテクチャ) NVIDIA

ダイ:約815mm2,トランジスタ:約210億個,性能:125テラFLOP/秒,消費電力300W

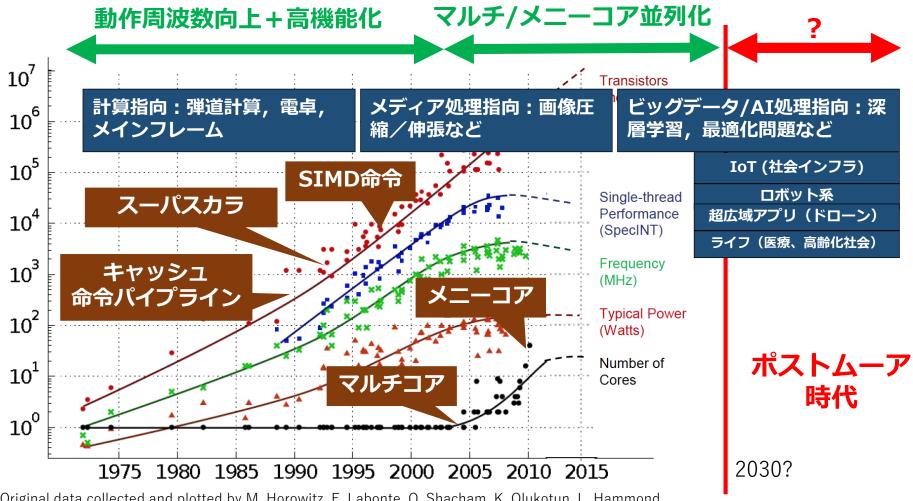

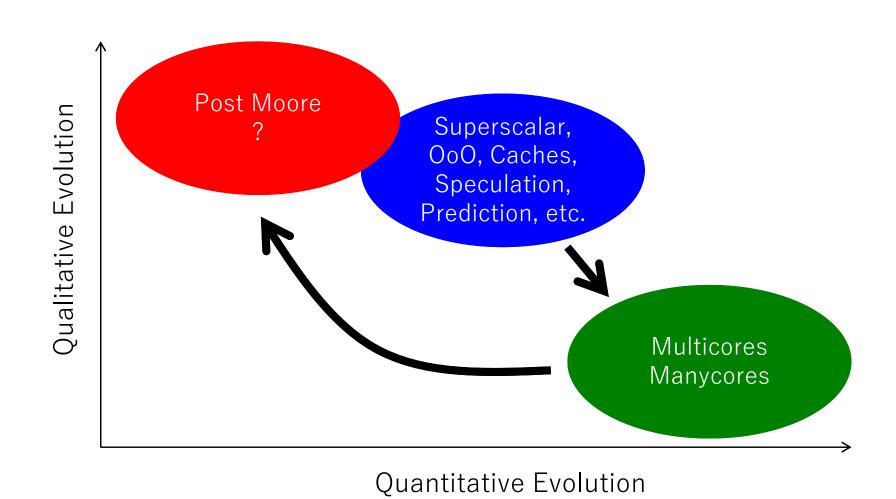

# 半導体微細化の終焉にどう立ち向かうか?

Original data collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten "Data Processing in ExaScale-Class Computer Systems," presented at the The Salishan Conference on High Speed Computing, 2011. Dotted line extrapolations by C. Moore.

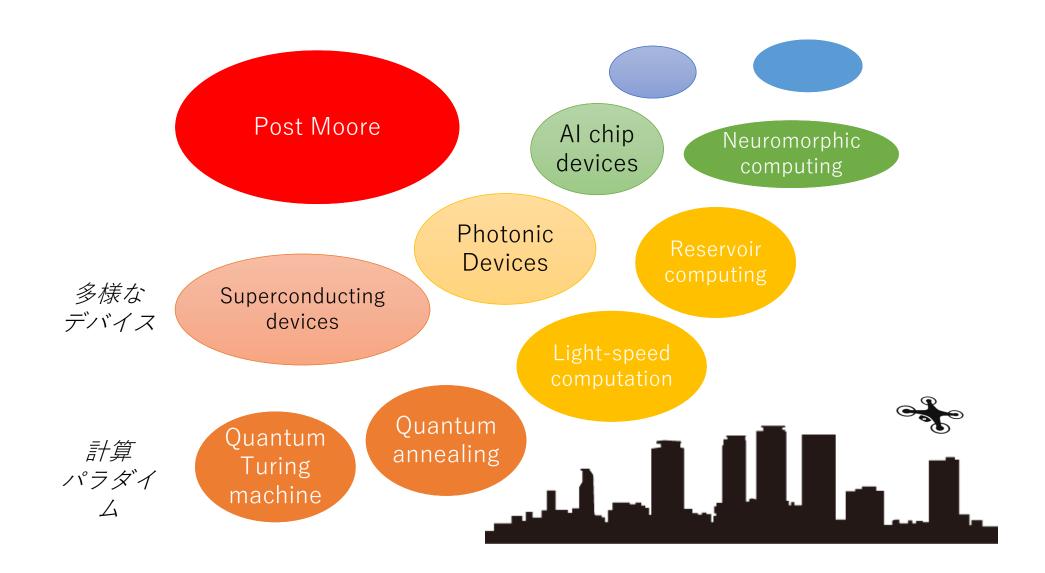

# 量的進化から質的進化へ!

# 次世代コンピュータの多様な可能性

# 重要な候補:量子コンピュータ

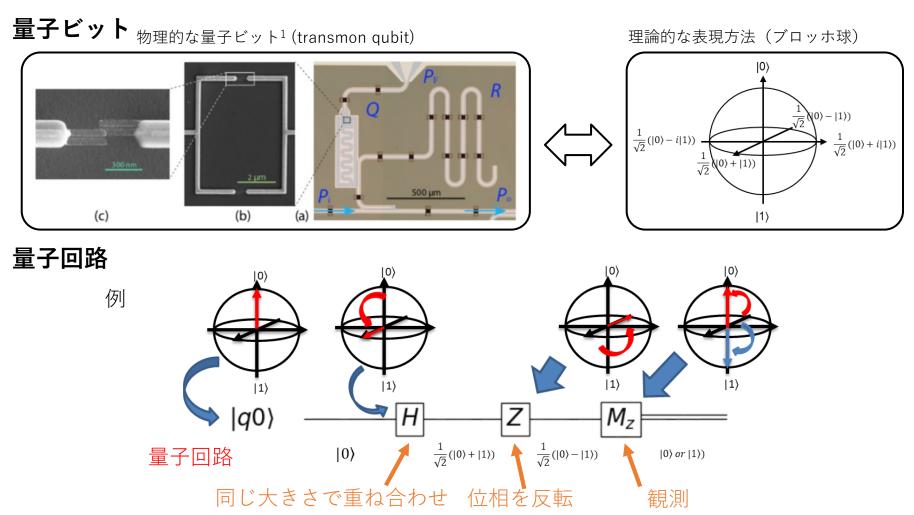

#### **ゲート方式量子コンピュータ** = 量子ビット $\times$ 量子回路

<sup>1</sup>X. Fu, et al, "An Experimental Microarchitecture for a Superconducting Qantum Processor," MICRO-50, 2017

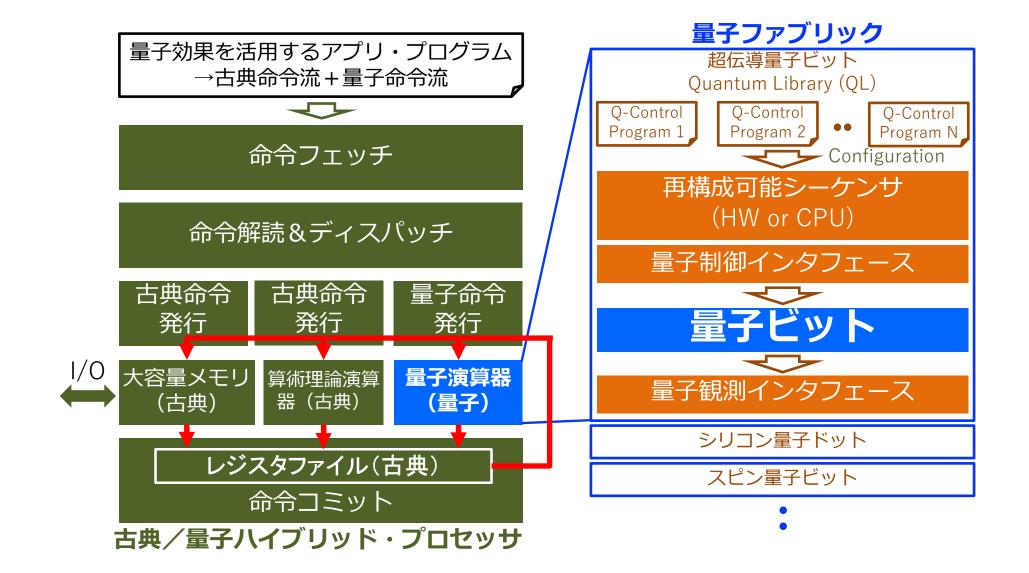

### 1方向性:古典一量子ハイブリッド・アーキテクチャ

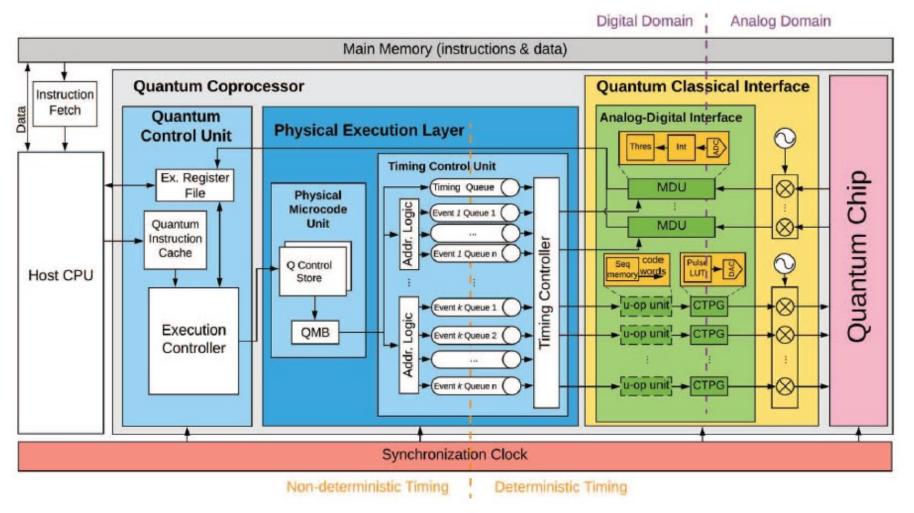

## 量子コンピュータ・システム・アーキテクチャ

<sup>1</sup>X. Fu, et al, "An Experimental Microarchitecture for a Superconducting Qantum Processor," MICRO-50, 2017

## 量子コンピュータ・システム・アーキテクチャ探求

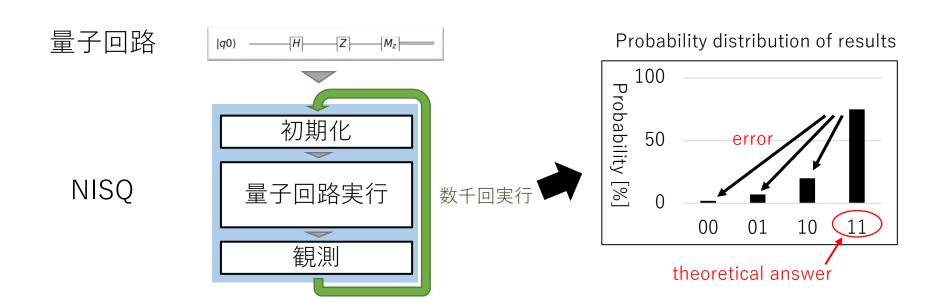

• Noisy Intermediate-Scale Quantum computer (NISQ)

トレー・エラーのため規模が制限される  $(50\sim1,000 \text{ qubits})$  エラーの影響を受ける  $2^{50}$ -次元のヒルベルト空間を状態として持つ

量子超越性 を有する可能性あり

(32 PB の容量に匹敵)

## アーキテクトから見た量子ゲートコンピュータ

### 重ね合わせによる 超並列計算

- ・計算量の質的変化

- ・NISQデバイス進歩

### 確率的な計算結果出力 (観測、ノイズ起因)

古典コンピュータにない特徴

#### 期待される応用

- ・組合せ最適化

- •量子化学計算

- 量子機械学習

### コンピュータとしての信頼性(再現性)

- ・信頼性:同じ入力に対して同じ出力が得られることを期待

- ・多数回実行して出力値ごとの出現確率(確率分布)を推定

- ・推定精度と実行回数(実行時間)にトレードオフが存在

# 解決すべき課題

量子ハードウェア

確率的な計算結果出力 (観測、ノイズ起因)

ほとんど考慮されていない

量子ソフトウェア

- ・qubitの物理特性

- ・量子ゲートの制御方法

- ・量子デバイスの入出力 (初期化、観測)

- ・応用上必要な推定精度

- ・出力結果の使い方

- ・アルゴリズムのエラー耐性

# 解決すべき課題

量子ハードウェア

量子アーキテクチャ

確率的ふるまいを考慮した 実行回数決定 量子ソフトウェア

ハードウェアの詳細を抽象化 (コンピュータ・アーキテクチャの役割)

必要な実行回数を考慮した 量子コンピュータのシステムレベル・モデル化と 設計上のトレードオフ探索が必要

## アプローチ

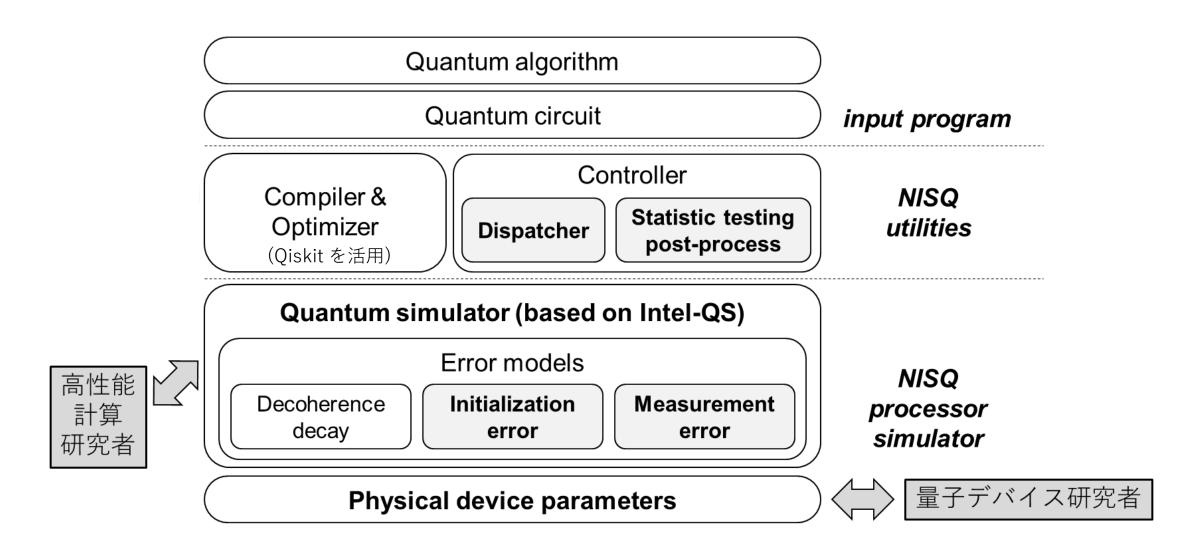

### 1. シミュレーションフレームワークの開発

コヒーレンス緩和、**初期化、観測エラー**を考慮 **/** モデル化およびパラメータ化 (超伝導量子ビットを想定)

### 2. 収束判定手法の構築

確率分布の**収束**を判定する条件を設定 **√** 確率分布がある有意水準である範囲に存在

### 3. 量子回路を用いたケーススタディ

量子アルゴリズムを用いた実験(今回は量子フーリエ変換) 量子ビットの忠実度と収束に必要な実行回数の関係を調査

## シミュレーション・フレームワーク

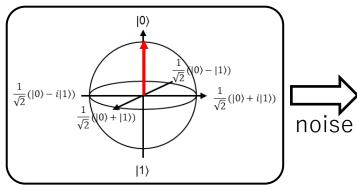

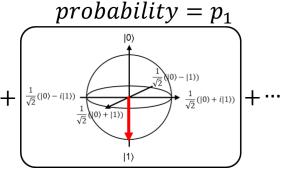

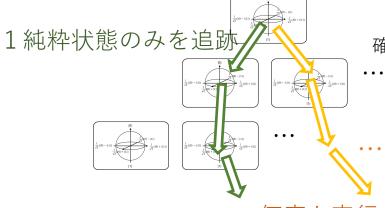

# エラーを含む量子ビットのシミュレーション

### モデル化

純粋状態

シミュレーション

time step

量子状態

混合状態

混合状態

確率に従って結果を変化させる

何度も実行

### 初期化及び観測エラーを考慮したシミュレーション

初期化および観測エラーを考慮した超伝導量子ビットシミュレーション (東京大学中村研究室と共同) 「Tanimoto+, IEEE ISVLSI OWS '20]

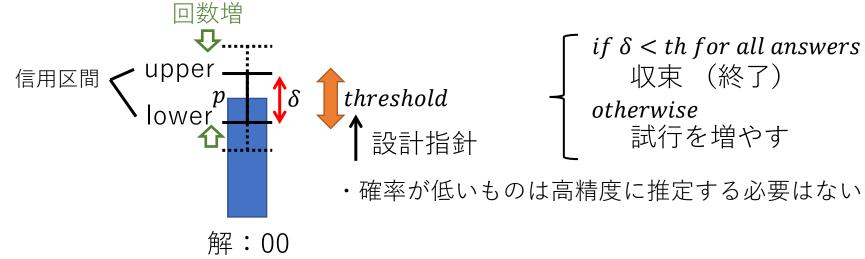

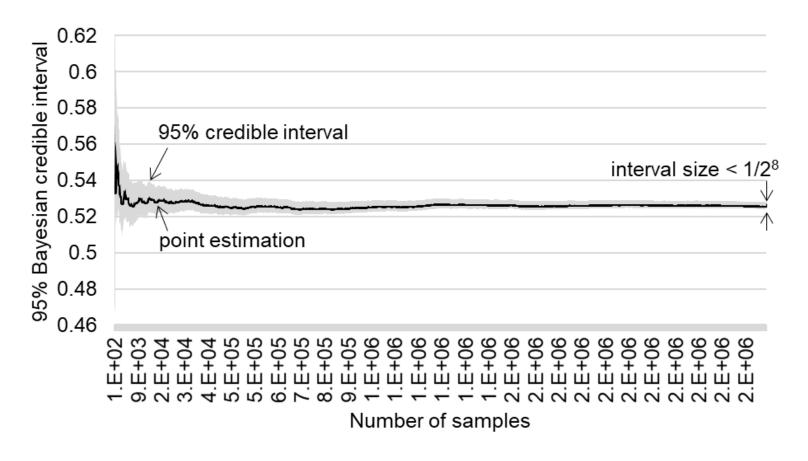

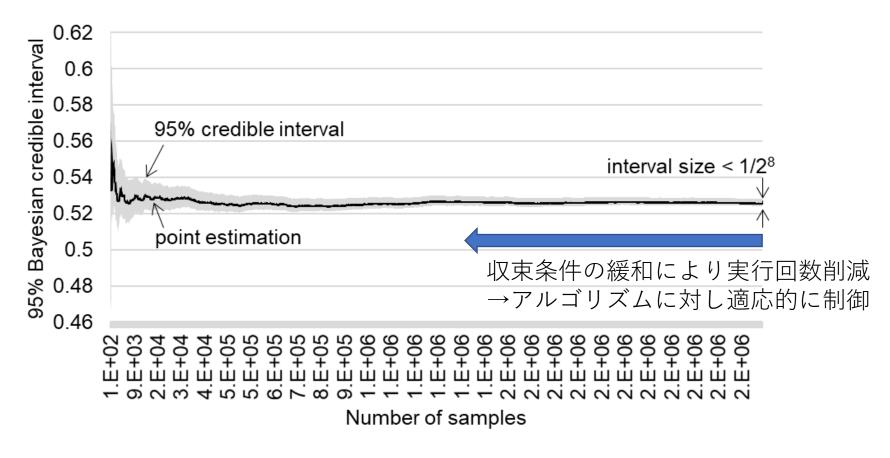

# 収束判定

確率分布が収束したかどうかの判定

### 判定方法

- 複数回の実行を多項分布とみなす

- ベイズ推定により各解の出現確率を推定

- 95%信用区間をあらかじめ設定した閾値と比較

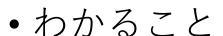

# 信用区間の予備評価

•信用区間:

CI(probability, #trials, a)

・以下を満たす最小の実行回数を調査

$CI(probability, \#trials, a) < \frac{1}{2} / \frac{1}{2}$

random case

- 1. 実行回数が最大となるのは probability = 0.5.

- 2. qubit数増に伴い実行回数増

- 3. 両端 (p=0, p=1付近) で急激に立ち上がる

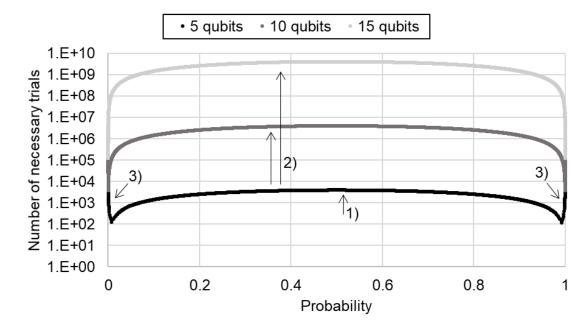

# NISQコンピュータの実行方法

- 基本方針

- 収束条件を設定(例: *CI* < <sup>1</sup>/<sub>2\*qubits</sub>)

- 有効な出力値を限定:

信用区間の下限  $> \frac{1}{2^{\#qubits}}$

- 実装

- 1. 最も収束条件の厳しい、|p-0.5| が最小となる出力値のみ収束判定

- 収束判定に必要な計算量を減らす

- 2. 収束後,有効な出力値のみを使う

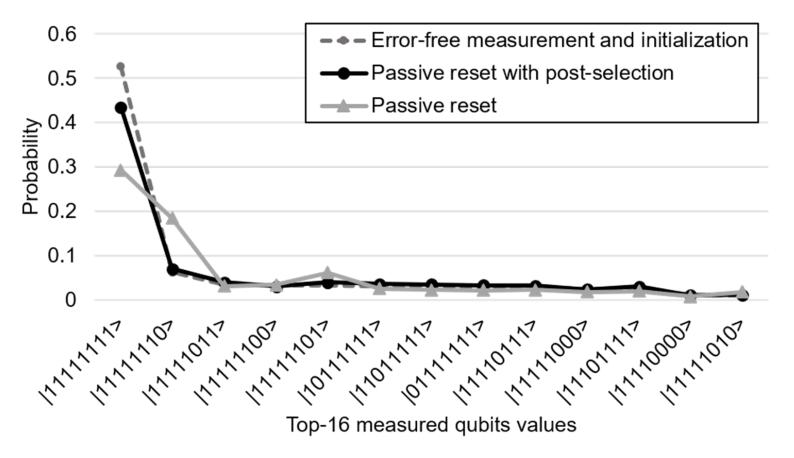

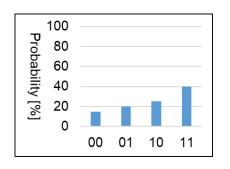

# 8量子ビットでの収束実験

ベイズ推定を用いた実行回数決定の様子 [Tanimoto+, IEEE ISVLSI QWS '20]

# 8量子ビットでの収束実験(シミュレーション)

ベイズ推定を用いた実行回数決定の様子 [Tanimoto+, IEEE ISVLSI QWS '20]

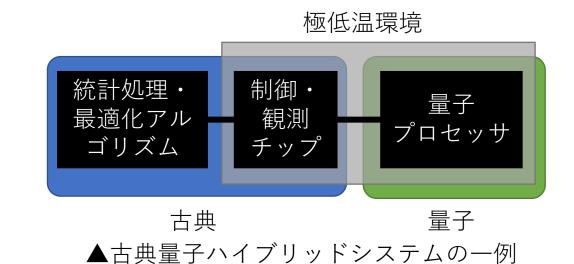

### 今後の展開:古典-量子ハイブリッド・システム探索

- 超伝導量子ビット:極低温環境(mK)で動作

- 古典-量子ハイブリッド・システム

- -量子コンピュータ自体ハイブリッド

- ーハイブリッド・アルゴリズム

- 古典処理の実行形態(例)

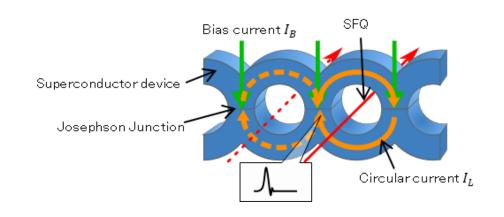

- 単一磁束量子 (SFQ)@4 K

- -CMOS@4 K, 77 K, 300 K

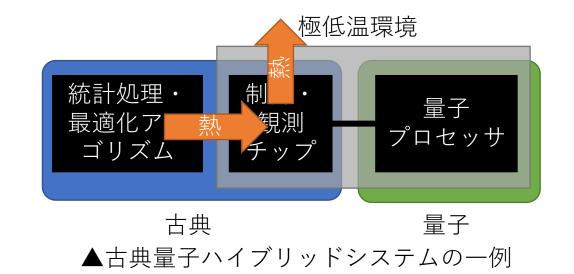

### 今後の展開:古典-量子ハイブリッド・システム探索

- 量子ビット:超伝導など極低温環境を要するものが多い

- 古典-量子ハイブリッド・システム

- -量子コンピュータ自体ハイブリッド

- ーハイブリッド・アルゴリズム

- 古典処理の実行形態 (例)

- 単一磁束量子 (SFQ)@4 K

- -CMOS@4 K, 77 K, 300 K

- 探索の目的

- 量子ビット数の大規模化に対応可能なアーキテクチャ

- 古典処理の動作温度, デバイスへのマッピング

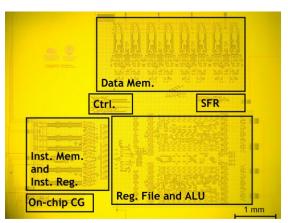

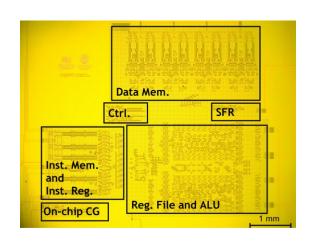

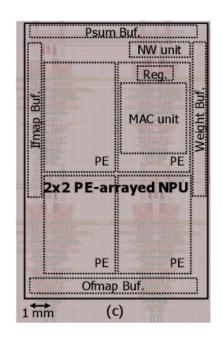

# SFQ回路の開発(名古屋大学と共同)

4-bit マイクロプロセッサ @ 53 GHz

$2 \times 2$  4-bit ニューラルネットワークアクセラレータ @ >50 GHz (sim)

#### その他演算器の設計

- · 浮動小数点演算器

- ・ベクトル演算器

## まとめ

- 計算機屋からみた量子コンピュータ - ポストムーア時代の質的変化をもたらすと期待

- 古典-量子ハイブリッド・コンピュータ

- 量子ビットの周辺回路を考えるとそれ自体がハイブリッド

- ーハイブリッド・アルゴリズム

- ・道具として使える(→再現性のある)コンピュータへーシステムレベルでのサポート:実行回数決定法の探究

- 今後の展開

- 動作環境を考慮した古典処理の設計空間探索